TPS51200QDRCRQ1 Circuitu integratu specializatu di gestione di l'alimentazione novu è originale

♠ Descrizzione di u pruduttu

| Attributu di u pruduttu | Valore di l'attributu |

| Fabbricante: | Texas Instruments |

| Categoria di u pruduttu: | Gestione di l'alimentazione specializata - PMIC |

| RoHS: | Dettagli |

| Serie: | TPS51200-Q1 |

| Tipu: | Automotivu |

| Stile di muntatura: | SMD/SMT |

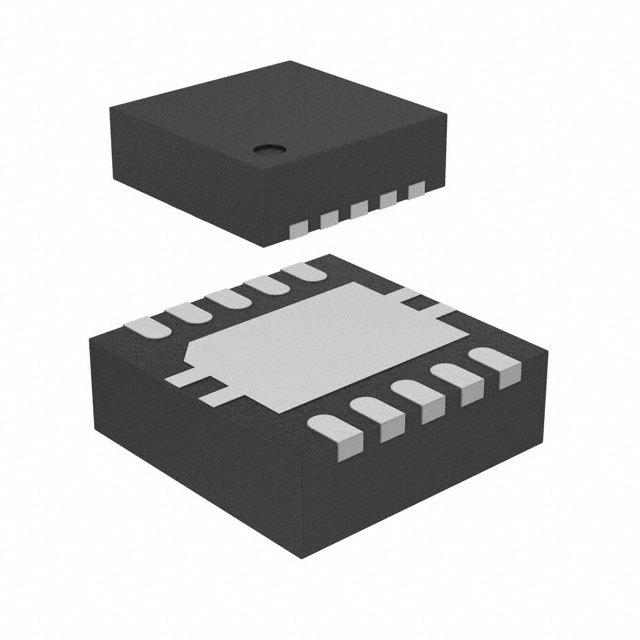

| Pacchettu / Custodia: | VSON-10 |

| Corrente di uscita: | 600 mA |

| Temperatura minima di funziunamentu: | - 40°C |

| Temperatura massima di funziunamentu: | + 125°C |

| Qualificazione: | AEC-Q100 |

| Imballaggio: | Bobina |

| Imballaggio: | Tagliate u nastro |

| Imballaggio: | MouseReel |

| Marca: | Texas Instruments |

| Sensibile à l'umidità: | Iè |

| Corrente di alimentazione operativa: | 700 uA |

| Pd - Dissipazione di putenza: | 0,79 W |

| Tipu di pruduttu: | Gestione di l'alimentazione specializata - PMIC |

| Quantità di pacchettu di fabbrica: | 3000 |

| Sottucateguria: | PMIC - Circuiti integrati di gestione di l'alimentazione |

| Pesu unitariu: | 0,001386 once |

♠TPS51200-Q1 Regulatore di terminazione DDR di dissipatore è fonte

U dispusitivu TPS51200-Q1 hè un regulatore di terminazione à doppia velocità di dati (DDR) sink and source specificamente cuncipitu per sistemi à bassa tensione d'ingressu, à bassu costu è à bassu rumore induve u spaziu hè una considerazione chjave. U dispusitivu TPS51200-Q1 mantene una risposta transitoria rapida è richiede solu una capacità di uscita minima di 20 μF. U dispusitivu TPS51200-Q1 supporta una funzione di telerilevamentu è tutti i requisiti di alimentazione per a terminazione di bus VTT DDR, DDR2, DDR3, DDR3L, Low Power DDR3 è DDR4.

Inoltre, u dispusitivu TPS51200-Q1 furnisce un signale PGOOD à drenaggiu apertu per monitorà a regulazione di l'output è un signale EN chì pò esse adupratu per scaricà VTT durante S3 (suspensione à RAM) per l'applicazioni DDR.

U dispusitivu TPS51200-Q1 hè dispunibule in u pacchettu VSON-10 termicamente efficiente, è hè classificatu

tramindui verdi è senza piombu. U dispusitivu hè specificatu da –40 °C à 125 °C.

• Qualificatu per applicazioni automobilistiche

• Guida di prova AEC-Q100 cù i seguenti risultati:

– Temperatura di u dispusitivu Gradu 1: da –40 °C à 125 °C Temperatura ambiente di funziunamentu

– Classificazione ESD di u dispusitivu HBM Livello 2

– Classificazione ESD di u dispusitivu CDM Livellu C4B

• Tensione d'entrata: Supporta 2,5-V Rail è 3,3-V Rail

• Gamma di tensione VLDOIN: da 1,1 V à 3,5 V

• U regulatore di terminazione sink/source include a compensazione di Droop

• Richiede una capacità di uscita minima di 20 μF (tipicamente 3 × 10 μF MLCC) per applicazioni di terminazione di memoria (DDR)

• PGOOD per monitorà a regulazione di a pruduzzione

• Ingressu EN

• L'ingressu REFIN permette un tracciamentu d'ingressu flessibile sia direttamente sia per mezu di u divisore di resistenza

• Teledetezione (VOSNS)

• Riferimentu bufferizatu ±10 mA (REFOUT)

• Avvio dolce integratu, UVLO è OCL

• Spegnimentu termicu

• Risponde à e specificazioni JEDEC di DDR, DDR2; Supporta applicazioni DDR3, DDR3L, DDR3 à bassa putenza è DDR4 VTT

• Pacchettu VSON-10 Cù Cuscinu Termicu Espostu

• Regulatore di terminazione di memoria per DDR, DDR2, DDR3, DDR3L, DDR3 è DDR4 à bassa putenza

• Notebook, Desktop, Server

• Telecomunicazioni è Datacom, Stazione Base GSM, LCDTV è PDP-TV, Fotocopiatrice è Stampante, Set-Top Box