TMS320C6674ACYPA Multicore Fix/Float Pt Dig Sig Proc

♠ Descrizzione di u pruduttu

| Attributu di u pruduttu | Valore di l'attributu |

| Fabbricante: | Texas Instruments |

| Categoria di u pruduttu: | Processori è cuntrolli di signali digitali - DSP, DSC |

| Prodottu: | DSP |

| Serie: | TMS320C6674 |

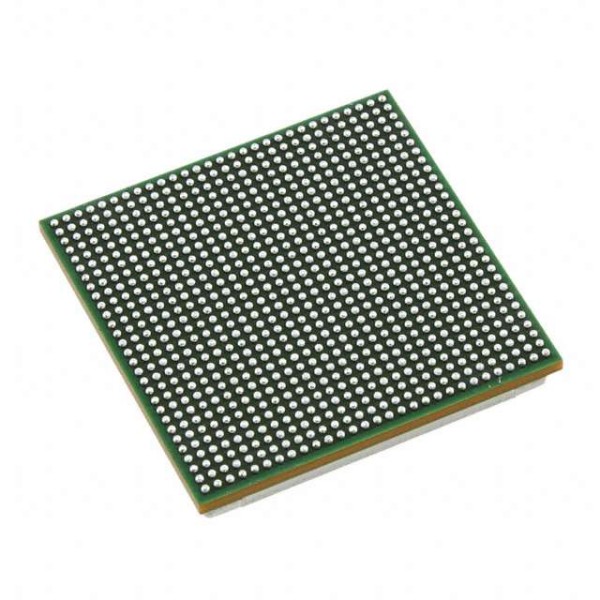

| Stile di muntatura: | SMD/SMT |

| Pacchettu / Custodia: | FCBGA-841 |

| Core: | C66x |

| Numeru di Core: | 4 Core |

| Frequenza massima di clock: | 1 GHz, 1,25 GHz |

| Memoria d'istruzzioni di a cache L1: | 4 x 32 kB |

| Memoria di dati di cache L1: | 4 x 32 kB |

| Dimensione di a memoria di u prugramma: | - |

| Dimensione di a RAM di dati: | - |

| Tensione di alimentazione operativa: | 900 mV à 1,1 V |

| Temperatura minima di funziunamentu: | - 40°C |

| Temperatura massima di funziunamentu: | + 100°C |

| Imballaggio: | Vassoio |

| Marca: | Texas Instruments |

| Larghezza di u bus di dati: | 8 bit/16 bit/32 bit |

| Tipu d'istruzione: | Puntu fissu/fluttuante |

| MMACS: | 160000 MMACS |

| Sensibile à l'umidità: | Iè |

| Numeru d'I/O: | 16 E/S |

| Numeru di Timer/Contatori: | 12 Cronometru |

| Tipu di pruduttu: | DSP - Processori è Controllori di Segnali Digitali |

| Quantità di pacchettu di fabbrica: | 44 |

| Sottucateguria: | Processori è cuntrolli integrati |

| Tensione di alimentazione - Max: | 1,1 V |

| Tensione di alimentazione - Min: | 900 mV |

| Pesu unitariu: | 0,173396 once |

♠ Processore di signali digitale multicore à virgola fissa è à virgola mobile

U DSP TMS320C6674 hè un DSP à virgola fissa/flottante di e più alte prestazioni basatu annantu à l'architettura multicore KeyStone di TI. Incorporendu u novu è innovativu core DSP C66x, questu dispositivu pò funziunà à una velocità di core finu à 1,25 GHz. Per i sviluppatori di una vasta gamma di applicazioni, cum'è sistemi critici per a missione, imaging medicale, test è automatizazione, è altre applicazioni chì richiedenu alte prestazioni, u DSP TMS320C6674 di TI offre un DSP cumulativu di 5 GHz è permette una piattaforma efficiente in termini di energia è faciule da aduprà. Inoltre, hè cumpletamente retrocompatibile cù tutti i DSP à virgola fissa è flottante esistenti di a famiglia C6000.

L'architettura KeyStone di TI furnisce una piattaforma programmabile chì integra diversi sottosistemi (core C66x, sottosistema di memoria, periferiche è acceleratori) è utilizza parechji cumpunenti è tecniche innovative per massimizà a cumunicazione intra-dispositivu è inter-dispositivu chì permette à e diverse risorse DSP di funziunà in modu efficiente è senza intoppi. Centrale à sta architettura sò cumpunenti chjave cum'è Multicore Navigator chì permette una gestione efficiente di i dati trà i vari cumpunenti di u dispositivu. TeraNet hè un switch fabric senza bloccu chì permette un muvimentu di dati internu rapidu è senza cuntesa. U controller di memoria condivisa multicore permette l'accessu à a memoria condivisa è esterna direttamente senza prelevà da a capacità di u switch fabric.

• Quattru sottosistemi core DSP TMS320C66x™ (C66x CorePacs), ognunu cù

– Core di CPU C66x à virgola fissa/flottante da 1,0 GHz o 1,25 GHz

› 40 GMAC/Core per puntu fissu à 1,25 GHz

› 20 GFLOP/Core per virgola mobile à 1,25 GHz

– Memoria

› 32K Byte L1P per Core

› 32K Byte L1D per Core

› 512K Byte Locale L2 Per Core

• Controller di memoria spartuta multicore (MSMC)

– Memoria SRAM MSM 4096KB spartuta da quattru CorePac DSP C66x

– Unità di Prutezzione di Memoria per MSM SRAM è DDR3_EMIF

• Navigatore Multicore

– 8192 Code di hardware multifunzione cù Queue Manager

– DMA basatu annantu à i pacchetti per trasferimenti senza sovraccaricu

• Coprocessore di rete

– L'acceleratore di pacchetti permette u supportu per

› Pianu di trasportu IPsec, GTP-U, SCTP, PDCP

› Pianu d'utilizatore L2 PDCP (RoHC, Cifratura aerea)

› Trasportu à velocità di cavu di 1 Gbps à 1,5 MPacchetti per seconda

– U mutore di accelerazione di sicurezza permette u supportu per

› IPSec, SRTP, 3GPP, Interfaccia Aerea WiMAX, è Sicurezza SSL/TLS

› ECB, CBC, CTR, F8, A5/3, CCM, GCM, HMAC, CMAC, GMAC, AES, DES, 3DES, Kasumi, SNOW 3G, SHA-1, SHA-2 (Hash di 256 bit), MD5

› Velocità di crittografia finu à 2,8 Gbps

• Periferiche

– Quattru corsie di SRIO 2.1

› Operazione 1.24/2.5/3.125/5 GBaud supportata per corsia

› Supporta I/O Diretta, Passaghju di Messagi

› Supporta quattru cunfigurazioni di ligame 1×, duie 2×, una 4×, è duie 1× + una 2×

– PCIe Gen2

› Porta unica chì supporta 1 o 2 corsie

› Supporta finu à 5 GBaud per corsia

– Iperligame

› Supporta cunnessione à altri dispositivi di architettura KeyStone chì furniscenu scalabilità di e risorse

› Supporta finu à 50 Gbaud

– Sottosistema di switch Gigabit Ethernet (GbE)

› Dui porti SGMII

› Supporta l'operazione 10/100/1000 Mbps

– Interfaccia DDR3 à 64 bit (DDR3-1600)

› Spaziu di memoria indirizzabile di 8 GB byte

– EMIF à 16 bit

– Dui porti seriali di telecomunicazioni (TSIP)

› Supporta 1024 DS0 per TSIP

› Supporta 2/4/8 corsie à 32.768/16.384/8.192 Mbps per corsia

– Interfaccia UART

– Interfaccia I²C

– 16 pin GPIO

– Interfaccia SPI

– Modulu Semaforu

– Dodici timer à 64 bit

– Trè PLL in chip

• Temperatura cummerciale:

– da 0°C à 85°C

• Temperatura estesa:

– -40°C à 100°C

• Sistemi critici per a missione

• Sistemi di calculu à alte prestazioni

• Comunicazioni

• Audio

• Infrastruttura Video

• Imaging

• Analitica

• Rete

• Trasfurmazione di i media

• Automatizazione Industriale

• Automatizazione è Cuntrollu di Prucessu