TMS320F2812PGFA Processori è cuntrolli di signali digitali DSP DSC Controllu di sigla digitale à 32 bit cù flash

♠ Descrizzione di u pruduttu

| Attributu di u pruduttu | Valore di l'attributu |

| Fabbricante: | Texas Instruments |

| Categoria di u pruduttu: | Processori è cuntrolli di signali digitali - DSP, DSC |

| RoHS: | Dettagli |

| Prodottu: | DSC |

| Serie: | TMS320F2812 |

| Nome cummerciale: | C2000 |

| Stile di muntatura: | SMD/SMT |

| Pacchettu / Custodia: | LQFP-176 |

| Core: | C28x |

| Numeru di Core: | 1 Core |

| Frequenza massima di clock: | 150 MHz |

| Memoria d'istruzzioni di a cache L1: | - |

| Memoria di dati di cache L1: | - |

| Dimensione di a memoria di u prugramma: | 256 kB |

| Dimensione di a RAM di dati: | 36 kB |

| Tensione di alimentazione operativa: | 1,9 V |

| Temperatura minima di funziunamentu: | - 40°C |

| Temperatura massima di funziunamentu: | + 125°C |

| Imballaggio: | Vassoio |

| Risoluzione ADC: | 12 bit |

| Marca: | Texas Instruments |

| Larghezza di u bus di dati: | 32 bit |

| Tensione I/O: | 3,3 V |

| Tipu d'istruzione: | Puntu fissu |

| Sensibile à l'umidità: | Iè |

| Tipu di pruduttu: | DSP - Processori è Controllori di Segnali Digitali |

| Quantità di pacchettu di fabbrica: | 40 |

| Sottucateguria: | Processori è cuntrolli integrati |

| Pesu unitariu: | 0,066886 once |

• Tecnulugia CMOS statica d'altu rendimentu

– 150 MHz (tempu di ciclu di 6,67 ns)

– Bassa putenza (nucleu di 1,8 V à 135 MHz,Core di 1,9 V à 150 MHz, cuncepimentu di 3,3 VI/O)

• Supportu di scansione di cunfini JTAG

– Norma IEEE 1149.1-1990 Norma IEEEPruvà u Portu d'Accessu è a Scansione di CunfiniArchitettura

• CPU à 32 bit d'alte prestazioni (TMS320C28x)

– Operazioni MAC 16 × 16 è 32 × 32

– 16 × 16 MAC duale

– Architettura di l'autobus di Harvard

– Operazioni atomiche

- Risposta è trasfurmazione rapida à l'interruzzione

– Modellu di prugrammazione di memoria unificatu

– Portata di l'indirizzu di u prugramma/dati lineare 4M

– Efficiente in termini di codice (in C/C++ è Assembly)

– Codice surghjente di u processore TMS320F24x/LF240xcumpatibile

• Memoria integrata in chip

– Finu à 128K × 16 flash(Quattru settori 8K × 16 è sei 16K × 16)

– ROM OTP 1K × 16

– L0 è L1: 2 blocchi di 4K × 16 ognunu SingleAccess RAM (SARAM)

– H0: 1 bloccu di 8K × 16 SARAM

– M0 è M1: 2 blocchi di 1K × 16 ognunu SARAM

• ROM d'avviu (4K × 16)

– Cù i modi d'avvio di u software

– Tabelle matematiche standard

• Interfaccia esterna (F2812)

– Più di 1M × 16 di memoria tutale

– Stati d'attesa programmabili

– Timing stroboscopicu di lettura/scrittura programmabile

– Trè selezzioni individuali di chip

• Endianità: Little endian

• Cuntrollu di l'orologio è di u sistema

– Oscillatore in chip

– Modulu di timer di guardia

• Trè interruzioni esterne

• Bloccu di Espansione d'Interruzione Periferica (PIE) chìsupporta 45 interruzioni periferiche

• Trè timer di CPU à 32 bit

• Chjave/serratura di sicurezza di 128 bit

– Prutege flash/OTP è L0/L1 SARAM

– Impedisce l'ingegneria inversa di u firmware

• Periferiche di cuntrollu di u mutore

– Dui Gestori d'Eventi (EVA, EVB)

– Compatibile cù i dispusitivi 240xA

• Periferiche di portu seriale

– Interfaccia Periferica Seriale (SPI)

– Dui interfacce di cumunicazione seriale (SCI),UART standard

– Rete di Zona di Cuntrollu Migliurata (eCAN)

– Porta seriale bufferizzata multicanale (McBSP)

• ADC à 12 bit, 16 canali

– Multiplexer d'entrata di canali 2 × 8

– Dui Campioni è Mantene

– Cunversioni singole/simultanee

– Velocità di cunversione rapida: 80 ns/12,5 MSPS

• Finu à 56 pin I/O d'usu generale (GPIO)

• Funzioni d'emulazione avanzate

– Funzioni d'analisi è di breakpoint

– Debugging in tempu reale via hardware

• Strumenti di sviluppu includenu

– Cumpilatore/assemblatore/linker ANSI C/C++

– Code Composer Studio™ IDE

– DSP/BIOS™

– Cuntrolli di scansione JTAG

• Norma IEEE 1149.1-1990 Norma IEEEPruvà u Portu d'Accessu è a Scansione di CunfiniArchitettura

• Modi di bassa putenza è risparmiu energeticu

– Modi IDLE, STANDBY, HALT supportati

– Disattivà l'orologi periferichi individuali

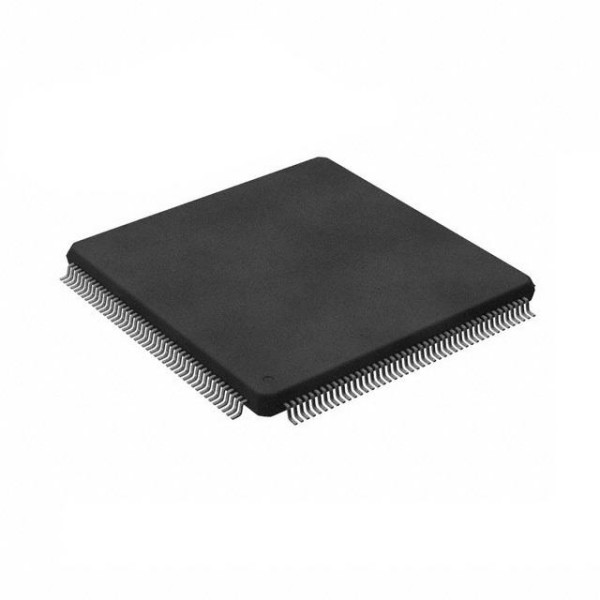

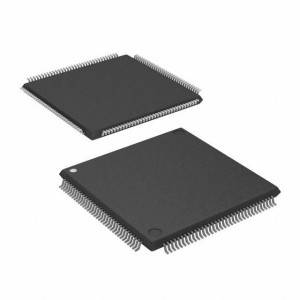

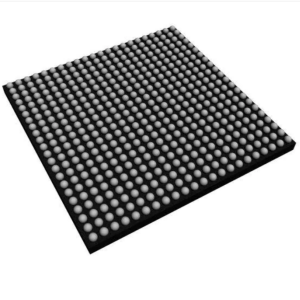

• Opzioni di pacchetti

– MicroStar BGA™ à 179 sfere cù memoria esternainterfaccia (GHH, ZHH) (F2812)

– Quad Flatpack à prufilu bassu à 176 pin (LQFP) cùinterfaccia di memoria esterna (PGF) (F2812)

– LQFP à 128 pin senza memoria esternainterfaccia (PBK) (F2810, F2811)

• Opzioni di temperatura

– A: da –40 °C à 85 °C (GHH, ZHH, PGF, PBK)

– S: da –40°C à 125°C (GHH, ZHH, PGF, PBK)

– Q: da –40°C à 125°C (PGF, PBK)(Qualificazione AEC-Q100 per l'automobile

applicazioni)

• Sistemi Avanzati di Assistenza à a Cunduttore (ADAS)

• Automatizazione di l'edificii

• Puntu di vendita elettronicu

• Veiculu elettricu/Veiculu elettricu ibridu (EV/HEV)gruppu motopropulsore

• Automatizazione di fabbrica

• Infrastruttura di rete

• Trasportu industriale

• Medicu, assistenza sanitaria è fitness

• Azionamenti di motori

• Erogazione di putenza

• Infrastruttura di telecomunicazioni

• Test è misurazione