XC6SLX25-2FTG256C FPGA – Array di porte programmabili in campu A fabbrica ùn accetta attualmente ordini per questu pruduttu.

♠ Descrizzione di u pruduttu

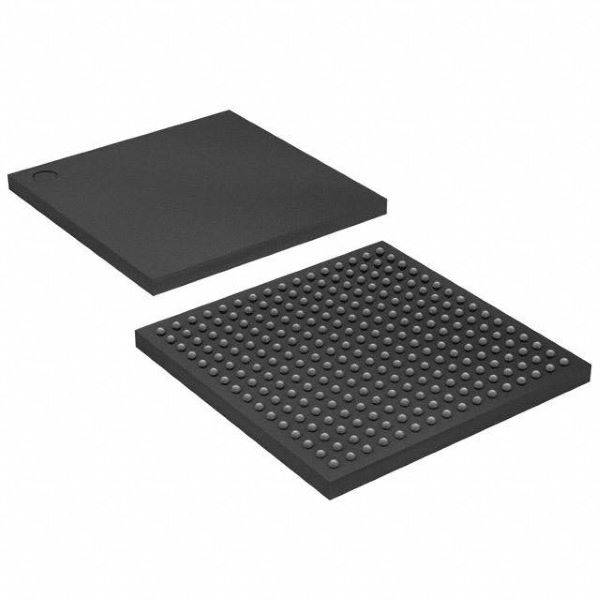

| Attributu di u pruduttu | Valore di l'attributu |

| Fabbricante: | Xilinx |

| Categoria di u pruduttu: | FPGA - Array di porte programmabili in campu |

| RoHS: | Dettagli |

| Serie: | XC6SLX25 |

| Numeru d'elementi logici: | 24051 LE |

| Numeru d'I/O: | 186 E/S |

| Tensione di alimentazione - Min: | 1,14 V |

| Tensione di alimentazione - Max: | 1,26 V |

| Temperatura minima di funziunamentu: | 0°C |

| Temperatura massima di funziunamentu: | + 85°C |

| Velocità di dati: | - |

| Numeru di Ricetrasmettitori: | - |

| Stile di muntatura: | SMD/SMT |

| Pacchettu/Casa: | FBGA-256 |

| Marca: | Xilinx |

| RAM distribuita: | 229 kbit |

| RAM à blocchi integrata - EBR: | 936 kbit |

| Frequenza massima di funziunamentu: | 1080 MHz |

| Sensibile à l'umidità: | Iè |

| Numeru di blocchi di matrice logica - LAB: | 1879 LAB |

| Tensione di alimentazione operativa: | 1,2 V |

| Tipu di pruduttu: | FPGA - Array di porte programmabili in campu |

| Quantità di pacchettu di fabbrica: | 1 |

| Sottucateguria: | Circuiti integrati di logica programmabile |

| Nome cummerciale: | Spartanu |

| Pesu unitariu: | 21,576 g |

♠ Panoramica di a famiglia Spartan-6

A famiglia Spartan®-6 furnisce capacità d'integrazione di sistemi di punta cù u costu tutale u più bassu per l'applicazioni di grande vulume. A famiglia di tredeci membri offre densità espanse chì varianu da 3.840 à 147.443 celle logiche, cù a metà di u cunsumu energeticu di e famiglie Spartan precedenti, è una connettività più rapida è cumpleta. Custruita nantu à una tecnulugia matura di prucessu di rame à bassa putenza di 45 nm chì furnisce l'equilibriu ottimale trà costu, putenza è prestazioni, a famiglia Spartan-6 offre una nova logica di tabella di ricerca (LUT) à 6 ingressi à doppiu registru più efficiente è una ricca selezzione di blocchi di livellu di sistema integrati. Questi includenu RAM à blocchi di 18 Kb (2 x 9 Kb), slice DSP48A1 di seconda generazione, controller di memoria SDRAM, blocchi di gestione di l'orologio in modalità mista migliorati, tecnulugia SelectIO™, blocchi di ricetrasmettitore seriale à alta velocità ottimizzati per a putenza, blocchi Endpoint compatibili cù PCI Express®, modalità avanzate di gestione di l'alimentazione à livellu di sistema, opzioni di cunfigurazione di rilevamentu automaticu è sicurezza IP migliorata cù prutezzione AES è Device DNA. Queste caratteristiche furniscenu una alternativa programmabile à bassu costu à i prudutti ASIC persunalizati cù una facilità d'usu senza precedenti. I FPGA Spartan-6 offrenu a megliu suluzione per i disinni logichi di grande vulume, i disinni DSP orientati à u cunsumadore è l'applicazioni integrate sensibili à i costi. I FPGA Spartan-6 sò a basa di siliciu programmabile per e piattaforme di cuncepimentu miratu chì furniscenu cumpunenti software è hardware integrati chì permettenu à i cuncettori di fucalizza nantu à l'innuvazione appena u so ciclu di sviluppu principia.

• Famiglia Spartan-6:

• Spartan-6 LX FPGA: Ottimizatu per a logica

• Spartan-6 LXT FPGA: Cunnessione seriale à alta velocità

• Cuncipitu per un costu bassu

• Parechji blocchi integrati efficienti

• Selezzione ottimizzata di standard I/O

• Cuscinetti sfalsati

• Imballaggi di plastica di grande vulume liati cù fili metallichi

• Bassa putenza statica è dinamica

• Prucessu di 45 nm ottimizatu per u costu è a bassa putenza

• Modu di spegnimentu in ibernazione per una putenza zero

• A modalità di suspensione mantene u statu è a cunfigurazione cù un risvegliu multi-pin, miglioramentu di u cuntrollu

• Tensione di core di 1.0V di putenza inferiore (FPGA LX, solu -1L)

• Tensione di core di 1,2 V à alte prestazioni (FPGA LX è LXT, gradi di velocità -2, -3 è -3N)

• Banchi d'interfaccia SelectIO™ multitensione è multistandard

• Finu à 1.080 Mb/s di velocità di trasferimentu di dati per I/O differenziale

• Unità di uscita selezziunabile, finu à 24 mA per pin

• Norme è protokolli da 3,3 V à 1,2 VI/O

• Interfacce di memoria HSTL è SSTL à bassu costu

• Cunfurmità cù u scambiu à caldu

• Velocità di variazione I/O regulabili per migliurà l'integrità di u signale

• Transceiver seriali GTP à alta velocità in i FPGA LXT

• Finu à 3,2 Gb/s

• Interfacce à alta velocità cumprese: Serial ATA, Aurora, 1G Ethernet, PCI Express, OBSAI, CPRI, EPON, GPON, DisplayPort è XAUI

• Bloccu Endpoint integratu per i disinni PCI Express (LXT)

• Supportu di tecnulugia PCI® à bassu costu cumpatibile cù a specificazione 33 MHz, 32 è 64 bit.

• Fette DSP48A1 efficienti

• Aritmetica è trasfurmazione di signali d'altu rendimentu

• Multiplicatore rapidu 18 x 18 è accumulatore 48-bit

• Capacità di pipelining è di cascading

• Pre-aghjunta per aiutà l'applicazione di u filtru

• Blocchi di Controller di Memoria Integrati

• Supportu DDR, DDR2, DDR3 è LPDDR

• Velocità di dati finu à 800 Mb/s (12,8 Gb/s di larghezza di banda di piccu)

• Struttura di bus multi-porta cù FIFO indipendente per riduce i prublemi di timing di cuncepimentu

• Risorse logiche abbundanti cù una capacità logica aumentata

• Supportu opzionale di registru à scorrimentu o RAM distribuita

• LUT efficienti à 6 input migliuranu e prestazioni è minimizanu a putenza

• LUT cù doppiu flip-flop per applicazioni centrate nantu à a pipeline

• RAM in blocchi cù una larga gamma di granularità

• RAM à blocchi veloci cù attivazione di scrittura in byte

• Blocchi di 18 Kb chì ponu esse prugrammati opzionalmente cum'è duie RAM di blocchi indipendenti di 9 Kb

• Clock Management Tile (CMT) per prestazioni migliorate

• Sonnore bassu, sincronizazione flessibile

• I gestori di l'orologio digitale (DCM) eliminanu l'alterazione di l'orologio è a distorsione di u ciclu di travagliu

• Cicli à bloccu di fase (PLL) per un clocking à bassu jitter

• Sintesi di frequenza cù multiplicazione, divisione è cambiamentu di fase simultanei

• Sedici reti di orologi mundiali à bassa asimmetria

• Cunfigurazione simplificata, supporta standard à bassu costu

• Cunfigurazione di rilevazione automatica à 2 pin

• Ampiu supportu di SPI di terze parti (finu à x4) è flash NOR

• Piattaforma Flash Xilinx ricca di funzioni cù JTAG

• Supportu MultiBoot per l'aghjurnamentu remotu cù parechji flussi di bit, utilizendu a prutezzione watchdog

• Sicurezza rinfurzata per a prutezzione di u disignu

• Identificatore unicu di DNA di u dispusitivu per l'autentificazione di u disignu

• Crittografia di flussu di bit AES in i dispositivi più grandi

• Trasfurmazione integrata più rapida cù un processore MicroBlaze™ soft miglioratu è à bassu costu

• Design di riferimentu è IP di punta