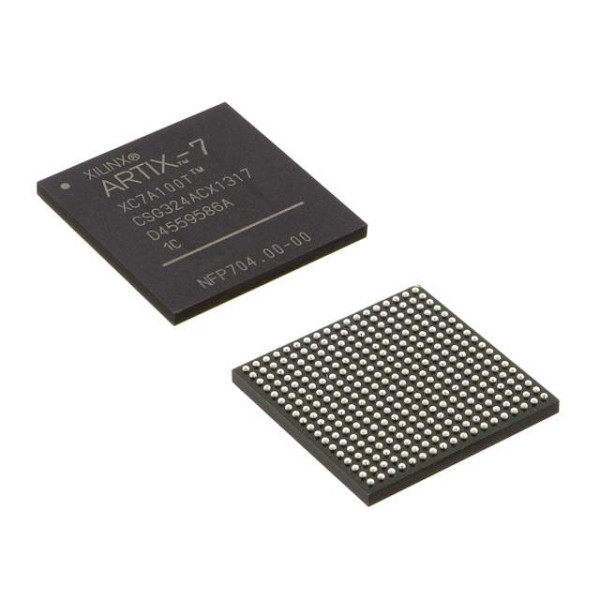

XC7A50T-2CSG324I FPGA – Array di porte programmabili in campu XC7A50T-2CSG324I

♠ Descrizzione di u pruduttu

| Attributu di u pruduttu | Valore di l'attributu |

| Fabbricante: | Xilinx |

| Categoria di u pruduttu: | FPGA - Array di porte programmabili in campu |

| Serie: | XC7A50T |

| Numeru d'elementi logici: | 52160 LE |

| Numeru d'I/O: | 210 E/S |

| Tensione di alimentazione - Min: | 0,95 V |

| Tensione di alimentazione - Max: | 1,05 V |

| Temperatura minima di funziunamentu: | - 40°C |

| Temperatura massima di funziunamentu: | + 100°C |

| Velocità di dati: | - |

| Numeru di Ricetrasmettitori: | - |

| Stile di muntatura: | SMD/SMT |

| Pacchettu / Custodia: | CSBGA-324 |

| Marca: | Xilinx |

| RAM distribuita: | 600 kbit |

| RAM à blocchi integrata - EBR: | 2700 kbit |

| Sensibile à l'umidità: | Iè |

| Numeru di blocchi di matrice logica - LAB: | 4075 LABORATORIU |

| Tensione di alimentazione operativa: | 1 V |

| Tipu di pruduttu: | FPGA - Array di porte programmabili in campu |

| Quantità di pacchettu di fabbrica: | 1 |

| Sottucateguria: | Circuiti integrati di logica programmabile |

| Nome cummerciale: | Artix |

| Pesu unitariu: | 1 oz |

♠ I FPGA di a serie Xilinx® 7 cumprendenu quattru famiglie di FPGA chì rispondenu à a gamma completa di requisiti di sistema, da applicazioni à bassu costu, cù un fattore di forma ridottu, sensibili à i costi è di grande vulume à larghezza di banda di connettività ultra high-end, capacità logica è capacità di elaborazione di signali per l'applicazioni ad alte prestazioni più esigenti.

I FPGA di a serie Xilinx® 7 cumprendenu quattru famiglie di FPGA chì rispondenu à a gamma completa di esigenze di sistema, da applicazioni à bassu costu, cù un fattore di forma ridottu, sensibili à i costi è di grande vulume à larghezza di banda di connettività ultra high-end, capacità logica è capacità di elaborazione di signali per l'applicazioni ad alte prestazioni più esigenti. I FPGA di a serie 7 includenu:

• Famiglia Spartan®-7: Ottimizzata per un costu ridottu, una putenza più bassa è prestazioni I/O elevate. Disponibile in un imballaggio à pocu costu è di fattore di forma assai ridottu per una impronta PCB minima.

• Famiglia Artix®-7: Ottimizzata per applicazioni à bassa putenza chì richiedenu transceiver seriali è un altu rendimentu DSP è logicu. Fornisce u costu tutale di a fattura di materiali più bassu per applicazioni à altu rendimentu è sensibili à i costi.

• Famiglia Kintex®-7: Ottimizzata per u megliu rapportu prezzu-prestazioni cù un miglioramentu 2X paragunatu à a generazione precedente, chì permette una nova classa di FPGA.

• Famiglia Virtex®-7: Ottimizzata per e più alte prestazioni è capacità di u sistema cù un miglioramentu di e prestazioni di u sistema di 2X. Dispositivi cù a più alta capacità abilitati da a tecnulugia di interconnessione di siliciu impilatu (SSI).

Custruiti nantu à una tecnulugia di prucessu HKMG (High-k Metal Gate) d'avanguardia, à alte prestazioni, à bassa putenza (HPL), 28 nm, i FPGA di a serie 7 permettenu un aumentu senza paragone di e prestazioni di u sistema cù 2,9 Tb/s di larghezza di banda I/O, una capacità di 2 milioni di celle logiche è un DSP di 5,3 TMAC/s, mentre cunsumanu u 50% in menu di energia rispetto à i dispositivi di a generazione precedente per offre una alternativa cumpletamente programmabile à l'ASSP è l'ASIC.

• Logica FPGA avanzata d'alte prestazioni basata annantu à a tecnulugia di tavule di ricerca (LUT) à 6 input reale, cunfigurabile cum'è memoria distribuita.

• RAM à blocchi à doppia porta di 36 Kb cù logica FIFO integrata per u buffering di dati in chip.

• Tecnulugia SelectIO™ d'alte prestazioni cù supportu per interfacce DDR3 finu à 1.866 Mb/s.

• Cunnessione seriale à alta velocità cù transceiver multi-gigabit integrati da 600 Mb/s à velocità massime di 6,6 Gb/s finu à 28,05 Gb/s, chì offre una modalità speciale à bassa putenza, ottimizzata per l'interfacce chip-to-chip.

• Un'interfaccia analogica configurabile da l'utente (XADC), chì incorpora dui convertitori analogicu-digitale 1MSPS à 12 bit cù sensori termichi è di alimentazione integrati in u chip.

• Fette DSP cù multiplicatore 25 x 18, accumulatore à 48 bit è pre-adder per un filtraggio ad alte prestazioni, cumpresu u filtraggio di coefficienti simmetrici ottimizzati.

• Tessere di gestione di l'orologio (CMT) putenti, chì combinanu blocchi di ciclu agganciatu à fase (PLL) è di gestione di l'orologio in modu mistu (MMCM) per alta precisione è jitter bassu.

• Implementà rapidamente u trattamentu integratu cù u processore MicroBlaze™.

• Bloccu integratu per PCI Express® (PCIe), per finu à x8 disinni di Endpoint è Root Port Gen3.

• Una larga varietà d'opzioni di cunfigurazione, cumprese u supportu per e memorie di massa, a crittografia AES à 256 bit cù l'autenticazione HMAC/SHA-256 è a rilevazione è a currezzione SEU integrata.

• Imballaggio flipchip à bassu costu, wire-bond, bare-die è flipchip à alta integrità di segnale chì offre una migrazione faciule trà i membri di a famiglia in u listessu pacchettu. Tutti i pacchetti sò dispunibili senza piombu è pacchetti selezziunati in opzione piombu.

• Cuncipitu per alte prestazioni è bassa putenza cù 28 nm, HKMG, prucessu HPL, tecnulugia di prucessu di tensione core 1.0V è opzione di tensione core 0.9V per una putenza ancu più bassa.