TMS320VC5509AZAY Processori è Controlleri di Segnu Digitale - DSP, DSC Processore di Segnu Digitale à Puntu Fissu 179-NFBGA -40 à 85

♠ Descrizzione di u produttu

| Attributu di u produttu | Valore di l'attributu |

| Produttore: | Texas Instruments |

| Categoria di produttu: | Processori è Controller di Segnale Digitale - DSP, DSC |

| RoHS: | Dettagli |

| Pruduttu: | DSP |

| Serie: | TMS320VC5509A |

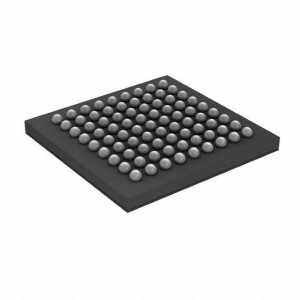

| Stile di muntatura: | SMD/SMT |

| Pacchettu / Casu: | NFBGA-179 |

| Core: | C55x |

| Numero di core: | 1 Core |

| Frequenza massima di clock: | 200 MHz |

| L1 Cache Instruction Memory: | - |

| Memoria di dati cache L1: | - |

| Dimensione di memoria di prugramma: | 64 kB |

| Dimensione RAM di dati: | 256 kB |

| Tensione di alimentazione operativa: | 1,6 V |

| Température minimale de fonctionnement : | - 40 C |

| Temperature Maximum Operating: | + 85 C |

| Imballaggio: | vassa |

| Marca: | Texas Instruments |

| Tipu d'istruzione: | Puntu Fissu |

| Tipu d'interfaccia: | I2C |

| Sensibili à l'umidità: | Iè |

| Tipu di pruduttu: | DSP - Processori è Controlleri di Segnu Digitale |

| Quantità di pacchettu di fabbrica: | 160 |

| Subcategoria: | Processori è Controllers Incrustati |

| Tensione di alimentazione - Max: | 1,65 V |

| Tensione di alimentazione - Min: | 1,55 V |

| Timer di Watchdog: | Watchdog Timer |

♠ TMS320VC5509A Processore di Segnale Digitale à Puntu Fissu

U TMS320VC5509A processore di signale digitale (DSP) à puntu fissu hè basatu annantu à u core di CPU di generazione TMS320C55x DSP.L'architettura C55x ™ DSP ottene un altu rendiment è una putenza bassa per mezu di un parallelismu aumentatu è un focus tutale nantu à a riduzione di a dissipazione di putenza.U CPU supporta una struttura di bus internu chì hè cumpostu di un bus di prugramma, trè busi di lettura di dati, dui bus di scrittura di dati, è busi supplementari dedicati à l'attività periferica è DMA.Questi autobus furniscenu a capacità di realizà finu à trè letture di dati è duie scritture di dati in un unicu ciclu.In parallelu, u controller DMA pò realizà finu à dui trasferimenti di dati per ciclu indipendentemente da l'attività di CPU.

U CPU C55x furnisce duie unità multiply-accumulate (MAC), ognuna capace di multiplicazione 17-bit x 17-bit in un unicu ciclu.Un'unità aritmetica/logica centrale a 40 bit (ALU) è supportata da una ALU addizionale a 16 bit.L'usu di l'ALU hè sottu u cuntrollu di l'istruzzioni, chì furnisce a capacità di ottimisà l'attività parallela è u cunsumu di energia.Queste risorse sò gestite in l'Unità di Indirizzu (AU) è l'Unità di Dati (DU) di a CPU C55x.

A generazione C55x DSP supporta un set di istruzioni di larghezza di byte variabile per una densità di codice mejorata.L'Unità di Istruzzioni (IU) eseguisce u prugramma di 32 bit da a memoria interna o esterna è mette in fila istruzioni per l'Unità di Programma (PU).L'Unità di prugramma decodifica l'istruzzioni, dirige i compiti à e risorse AU è DU, è gestisce a pipeline cumplettamente protetta.A capacità di ramificazione predittiva evita i flussi di pipeline nantu à l'esecuzione di istruzzioni cundiziunali.

E funzioni di input è output di u scopu generale è l'A/D a 10 bit furniscenu pin sufficienti per u statu, interruzioni è bit I/O per LCD, tastiere è interfacce media.L'interfaccia parallela opera in dui modi, sia cum'è schiavu à un microcontroller cù u portu HPI o cum'è interfaccia media parallela utilizendu l'EMIF asincronu.I media seriali sò supportati da duie periferiche MultiMedia Card/Secure Digital (MMC/SD) è trè McBSP.

U settore perifericu 5509A include una interfaccia di memoria esterna (EMIF) chì furnisce l'accessu glueless à e memorie asincrone cum'è EPROM è SRAM, è ancu à memorie d'alta velocità è d'alta densità cum'è DRAM sincrona.Peripherals supplementari include Universal Serial Bus (USB), clock in tempu reale, watchdog timer, I2C multi-master è interfaccia slave.Trè porti seriali di buffer multicanale full-duplex (McBSP) furniscenu una interfaccia glueless à una varietà di dispositi seriali standard di l'industria, è una cumunicazione multicanale cù finu à 128 canali abilitati separatamente.L'interfaccia di u portu di l'ospite (HPI) hè una interfaccia parallela di 16 bit utilizata per furnisce l'accessu à u processore host à 32K bytes di memoria interna nantu à u 5509A.L'HPI pò esse cunfiguratu in modu multiplexed o non-multiplexed per furnisce una interfaccia glueless à una larga varietà di processori ospiti.U controller DMA furnisce u muvimentu di dati per sei cuntesti di canali indipendenti senza intervenzione di CPU, furnisce un throughput DMA di finu à duie parole di 16 bit per ciclu.Sò ancu inclusi dui timers per u scopu generale, finu à ottu pin I/O per scopi generali (GPIO) dedicati, è a generazione di clock digitale in fase-locked loop (DPLL).

U 5509A hè supportatu da u premiatu eXpressDSP™, Code Composer Studio™ Integrated Development Environment (IDE), DSP/BIOS™, standard di l'algoritmu di Texas Instruments, è a più grande rete di terze parti di l'industria.L'IDE di Code Composer Studio presenta strumenti di generazione di codice cumpresi un compilatore C è Visual Linker, simulatore, RTDX™, driver di emulazione XDS510™, è moduli di valutazione.U 5509A hè ancu supportatu da a Biblioteca C55x DSP chì presenta più di 50 kernels di software di fundazione (filtri FIR, filtri IIR, FFT, è diverse funzioni matematiche) è ancu librerie di supportu di chip è board.

U core TMS320C55x DSP hè statu creatu cù una architettura aperta chì permette l'aghjunzione di hardware specificu per l'applicazione per rinfurzà u rendiment nantu à algoritmi specifichi.L'estensioni di hardware nantu à u 5509A ghjunghjenu l'equilibriu perfettu di u funziunamentu di a funzione fissa cù una flessibilità programabile, mentre ottene u cunsumu di bassa energia, è u costu chì tradiziunale hè statu difficiule di truvà in u mercatu di video-processori.L'estensioni permettenu à u 5509A di furnisce un rendimentu eccezziunale di codec video cù più di a mità di a so larghezza di banda dispunibule per eseguisce funzioni supplementari cum'è a cunversione di u spaziu di culore, l'operazioni di l'interfaccia d'utilizatore, a sicurità, TCP / IP, u ricunniscenza di voce è a cunversione di testu à voce.In u risultatu, un unicu 5509A DSP pò alimentà a maiò parte di l'applicazioni di video digitale portatili cù un spaziu di prucedura per risparmià.Per più infurmazione, vede l'Estensioni Hardware TMS320C55x per l'Applicazioni Image / Video Riferimentu di u Programmatore (numeru di letteratura SPRU098).Per più infurmazione nantu à l'usu di a Biblioteca di Trattamentu di l'Image DSP, vede a Riferimentu di u Programmatore di Biblioteche di Trattamentu di Image / Video TMS320C55x (numeru di letteratura SPRU037).

• Processore di signale digitale TMS320C55x™ d'alta prestazione, bassa putenza, puntu fissu

− 9.26-, 6.95-, 5-ns Tempu di ciclu di istruzzioni

− 108-, 144-, 200-MHz Clock Rate

− Una/Dui Instruction(s) Eseguita per Ciclu

− Dual Multipliers [Finu à 400 Million Multiply-Accumulates per Second (MMACS)]

− Due unità aritmetiche/logiche (ALU)

− Trè busi di lettura di dati / operandu interni è dui bus di scrittura di dati / operandu interni

• 128K x 16-Bit On-Chip RAM, Cumpostu da:

− 64K Byte di RAM à Doppiu Accessu (DARAM) 8 Blocchi di 4K × 16-Bit

− 192K Byte di RAM à Accessu Unicu (SARAM) 24 Blocchi di 4K × 16-Bit

• 64K Bytes di ROM One-Wait-State On-Chip (32K × 16-Bit)

• 8M × 16-Bit Massima Spaziu di Memoria Esterna Addressable (DRAM sincrona)

• Memoria di Bus Parallela Esterna 16-Bit Supporta Sia:

− Interfaccia di memoria esterna (EMIF) cù capacità GPIO è interfaccia senza colla per:

− RAM statica asincrona (SRAM)

− EPROM asincrona

- DRAM sincrona (SDRAM)

− Interfaccia Host-Port Enhanced Parallel 16-Bit (EHPI) cù capacità GPIO

• Cuntrolla Programmable Low-Power di Sei Duminii Funziunali Dispositivi

• On-Chip Scan-Based Emulation Logic

• On-Chip Peripherals

− Dui Timer 20-Bit

− Watchdog Timer

− Controller d'accessu direttu à a memoria di sei canali (DMA).

− Trè porti seriali chì supportanu una cumminazione di:

− Finu à 3 Porti Serial Buffered Multicanale (McBSP)

− Finu à 2 interfacce MultiMedia/Secure Digital Card

− Generatore di Clock Loop Locked Programmable Phase-Locked

− Sette (LQFP) o ottu (BGA) Pin I/O (GPIO) General Purpose è un Pin Output General Purpose (XF)

− Port Slave USB Full-Speed (12 Mbps) Supporta Trasferimenti Massivi, Interrupti è Isocroni

− Circuitu Inter-Integrated (I2C) Interfaccia Multi-Master è Slave

−Clock in Tempu Reale (RTC) Cù Input Crystal, Dominiu Clock Separatu, Alimentazione Separata

− 4-Channel (BGA) o 2-Channel (LQFP) 10-Bit Successive Approssimazione A/D

• IEEE Std 1149.1† (JTAG) Boundary Scan Logic

• Pacchetti :

− 144-Terminal Low-Profile Quad Flatpack (LQFP) (PGE Suffix)

− 179-Terminal MicroStar BGA™ (Ball Grid Array) (suffissu GHH)

− 179-Terminal senza piombo MicroStar BGA™ (Matrice di griglia di sfera) (Suffissu ZHH)

• Core 1.2-V (108 MHz), 2.7-V - 3.6-VI/Os

• Core 1.35-V (144 MHz), 2.7-V - 3.6-VI/Os

• Core 1.6-V (200 MHz), 2.7-V - 3.6-VI/Os

• Sistema ibridu, elettricu è di trenu di putenza (EV/HEV)

- Sistema di gestione di a batteria (BMS)

- Caricatore à bordu

- Inverter di trazione

- Convertitore DC/DC

- Starter / generatore